# CISCO SYSTEMS

# csco\_addrmap eVC Overview

Joseph H. Zhang July 2006

#### **Agenda**

- Motivation

- Theory of Operation

- Usage Model

- Legacy Support

#### **Motivation**

- Efficient register map modeling.

- Easily supports 25K register and memory entries.

- Current ASIC register space is approaching 10K entries.

- Support for vertical reuse.

- Interface independent CPU transaction interface.

- Hierarchical name scopes.

- Enables early testing of DUT.

- Automatic shadow value tracking and scoreboarding.

- Predefined sequence library.

- REG\_POR, WALKO/WALK1, INTERMIX, etc...

- \*\* Predefined register access functional coverage.

## **Theory of Operation - Architecture**

#### Theory of Operation – Register Modeling

- Efficient memory usage:

- All register and field instances are of the same exact type

no 'when' sub-typing.

- Register and field instances are uniquely identified via string names.

- Hierarchical name space:

- Each sequence/transaction has a user configurable scope to ensure vertical reuse.

- Three types of address map entries:

- Register : list of fields.

- Symbolic Memory: multiple rows of fields, where all rows have the same list of fields.

- Byte Memory: No logical fields, purely byte based memory with configurable Endianness.

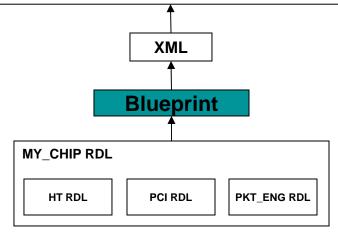

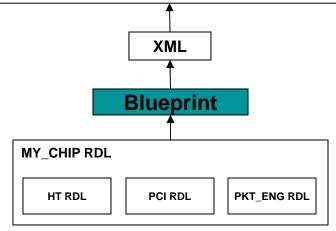

# Theory of Operation - Tight Integration with REGTOOL (Blueprint)

- Full support for all Blueprint components.

- Dynamic XML parser reduces HVL code base.

- Extensible architecture to support any register automation tool.

| Blueprint         | csco_addrmap                                                                           |  |

|-------------------|----------------------------------------------------------------------------------------|--|

| Field             | csco_addrmap_field_s                                                                   |  |

| Register          | csco_addrmap_reg_entry_s                                                               |  |

| Register<br>Array | csco_addrmap_symb_mem_entry_s                                                          |  |

| Register File     | csco_addrmap_name_scope_s                                                              |  |

| Address<br>Map    | csco_addrmap_name_scope_s csco_addrmap_physical_region_s csco_addrmap_logical_region_s |  |

| Side-Effects      | csco_addrmap_side_effect_t                                                             |  |

| Access<br>Modes   | csco_addrmap_sw_access_t                                                               |  |

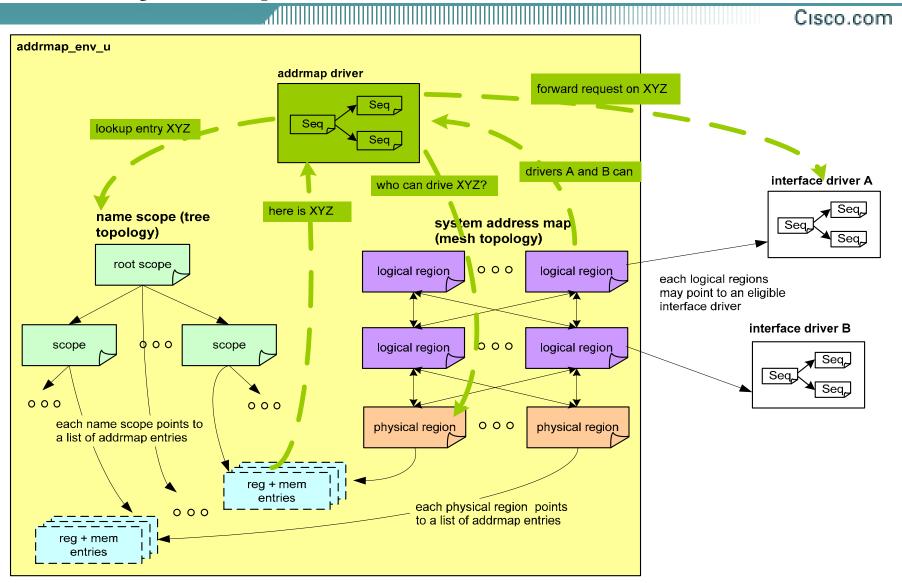

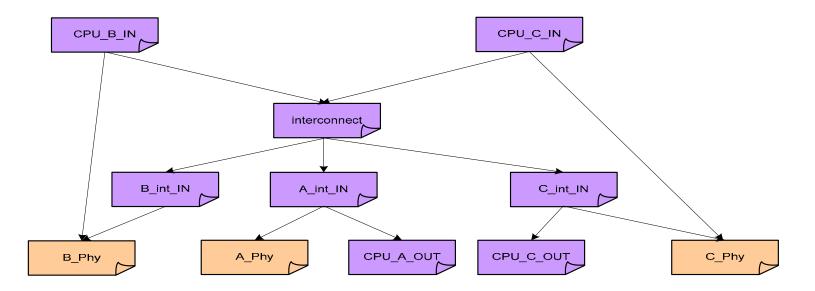

#### Theory of Operation – Address Map Modeling

Cisco.com

#### Physical region:

A container for a group of physical entries each with a unique local offset.

#### Logical region:

- Contains one or more child physical or logical regions.

- Amalgamate child regions which are accessed via the same interface.

- Logical grouping of child regions for ease of manipulation.

- Contains at most 1 pointer to a sequence driver that drives its interface.

- Configurable/extensible algorithm for assigning offsets to child regions.

#### **Theory of Operation – Address Map Modeling**

#### **Theory of Operation - Sequence Interface**

- Automatic/random transaction forwarding to source interface driver based on address map.

- Built-in segmentation engine (iterator) to map addrmap transaction to arbitrary interface alignments.

- Per-interface sequence backpressure no driver head-of-line blocking.

- Two addressing schemes:

- ENTRY: caller specifies entry/field names and values.

- OFFSET: caller specifies target region and numeric offset.

- Special macro, 'addrmap\_do', replaces Specman 'do' syntax.

#### **Theory of Operation - Sequence Flow Control**

Cisco.com **Addrmp Driver Only sequence** status = busy threads targetting busy drivers are intf-driver-1 blocked. Seq . а r b Seq Seq Seq intf-driver-1 Seq status = ready

Seq

Seq

### Posted versus Blocking

Cisco.com

|                              | resp_kind = POSTED                                             | resp_kind = NON_POSTED                                           |

|------------------------------|----------------------------------------------------------------|------------------------------------------------------------------|

| blocking_kind = NON_BLOCKING | addrmap_do returns in 0 time.                                  | addrmap_do returns in 0 time.                                    |

| blocking_kind =<br>BLOCKING  | addrmap_do returns once request has been transmitted over bus. | addrmap_do returns once response has been sent over request bus. |

Uses linking mechanism defined in csco\_trans package to detect transaction progress through system.

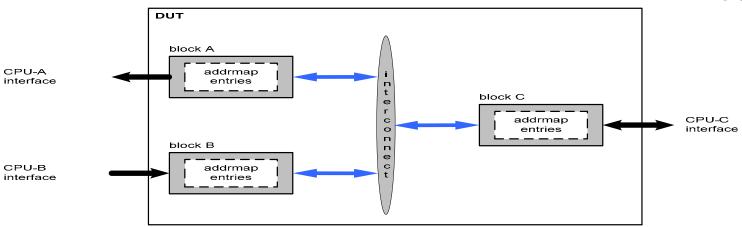

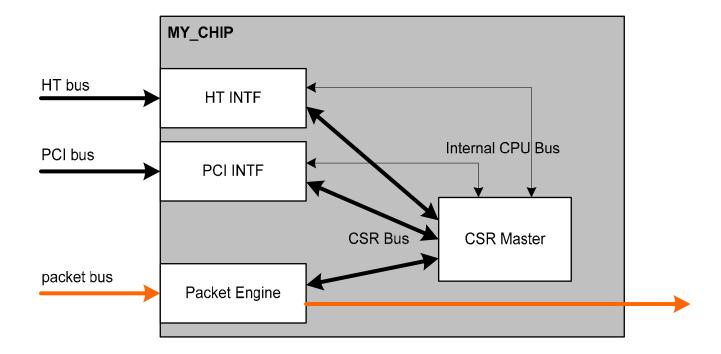

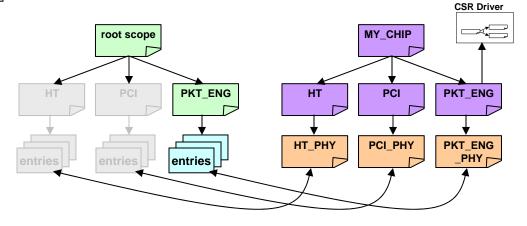

# **Usage Model – Example DUT**

# **Usage Model – Integrating Blueprint**

Cisco.com

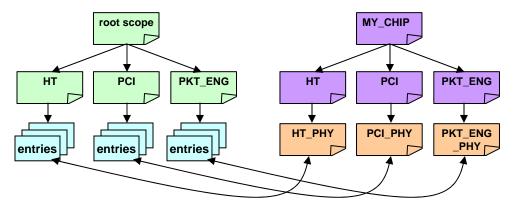

#### **Unit-Level**

```

extend MY_CHIP csco_addrmap_env_u {

post_generate() is also {

scope.trim_all_except("/PKT_ENG/");

};

};

```

PKT\_ENG unit bench specific logic

can be any regular expression

extend MY\_CHIP csco\_addrmap\_env\_u {

!bp\_region : csco\_addrmap\_logical\_region\_s;

post\_generate() is also {

bp\_region = scope.populate\_from\_xml\_file("MY\_CHIP.xml", NULL);

};

};

# **Usage Model – Integrating Blueprint**

Cisco.com

```

extend MY_CHIP csco_addrmap_env_u {

connect pointers() is also {

var blk_region := bp_region.get_region_first_match("PKT_ENG");

blk_region.set_eligible_driver(tb_ptr.csr_master.driver);

```

```

Unit-Level

```

Add access to registers via CSR bus.

```

extend MY_CHIP csco_addrmap_env_u {

post generate() is also {

scope.trim_all_except("/PKT_ENG/");

```

PKT ENG unit bench specific logic

can be any regular expression

extend MY\_CHIP csco\_addrmap\_env\_u { !bp\_region : csco\_addrmap\_logical\_region\_s; post\_generate() is also { bp\_region = scope.populate\_from\_xml\_file("MY\_CHIP.xml", NULL); **}**; **}**;

common\_top.e file - same logic for all testbenches.

}; **}**;

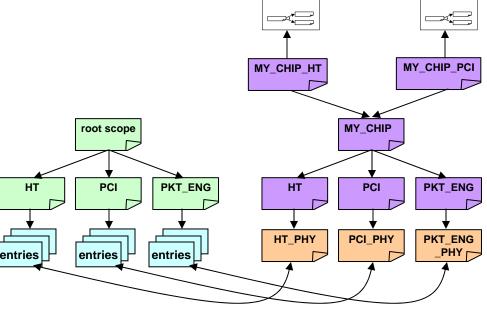

# **Usage Model – Integrating Blueprint**

Cisco.com

PCI driver

```

extend MY_CHIP csco_tb_u {

connect_pointers() is also {

var bp_region := addrmap.as_a(MY_CHIP csco_addrmap_env_u).blueprint_logical_region;

ht_env.set_addrmap_region(bp_region);

};

};

```

```

Chip-Level

```

```

extend MY_CHIP csco_tb_u {

connect_pointers() is also {

var bp_region := addrmap.as_a(MY_CHIP csco_addrmap_env_u).blueprint_logical_region;

pci_env.set_addrmap_region(bp_region);

};

};

```

Add access to registers via PCI interface.

HT driver

```

extend MY_CHIP csco_addrmap_env_u {

!bp_region : csco_addrmap_logical_region_s;

post_generate() is also {

bp_region = scope.populate_from_xml_file("MY_CHIP.xml", NULL);

};

};

root scope

XML

PCI

Blueprint

MY_CHIP RDL

entries

entries

HT RDL

PCI RDL

PKT ENG RDL

```

## **Usage Model – Sequence Interface**

```

extend csco addrmap seg kind t : [PKT ENG CFG];

extend PKT ENG CFG csco addrmap seq {

Error will result if normal 'do' is used

pcfg: pkt eng config s;

body() @driver.clock is also {

addrmap do WRITE entry trans keeping {

.resp kind == NON POSTED;

'entry_trans' is a predefined field

.return == BLOCKING;

.entry == "RING SIZE";

.fields == { .set_field("Ingress", pcfg.ig_ring_size);

.set field("Egress", pcfg.eg ring size) };

};

addrmap do WRITE entry trans keeping {

.entry == "RING CTRL";

.fields == { .set_field("Enable", 1) };

};

};

```

#### **Usage Model – Interface Driver**

Cisco.com

called by addrmap driver to forward transactions to interface driver.

Only accept 1 addrmap transaction at a time.

### **Usage Model – Interface Driver**

```

Cisco.com

extend csco_pci_trans_seq_kind_t : [ CSCO_ADDRMAP ];

extend CSCO ADDRMAP csco pci trans seq {

!addrmap_trans : CSCO_PCI'interface csco_addrmap_trans_s;

event addrmap_trans_ready;

package !addrmap segment : csco addrmap trans s;

wait for new addrmap transaction

body() @driver.clock is {

while(TRUE) {

if(addrmap_trans == NULL) {

sync @addrmap_trans_ready;

};

addrmap_segment = addrmap_trans.intf_iterator.get_next_segment();

addrmap trans.tracking.incr exp child cnt(1);

loop through all segments

while addrmap_segment != NULL {

returned by addrmap iterator

do pci_trans keeping {

<constrain addrmap segment fields to local transaction fields>;

};

each segment is just another

cprocess response if read>;

addrmap transaction

addrmap_segment = addrmap_trans.intf_iterator.get_next_segment();

if addrmap_segment != NULL {

addrmap trans.tracking.incr exp child cnt(1);

};

addrmap trans.tracking.link trans(one trans);

};

signal that we're ready for another

addrmap_trans = NULL;

addrmap transaction

};

};

```

Base Env

## **Usage Model – Configuring Iterator**

Cisco.com

```

extend CSCO_SPABUS'interface csco_addrmap_logical_region_s {

keep legal_alignments.size() == 3;

keep for each (la) in legal_alignments

index == 0 => all of {

la.alignment == 4;

la.max size == 4;

la.mask_precision == 4;

};

index == 1 => all of {

la.alignment == 2;

la.max size == 2;

la.mask_precision == 2;

};

index == 2 => all of {

la.alignment == 1;

la.max_size == 1;

la.mask_precision == 1;

};

};

```

There can be multiple legal alignments per interface. The addrmap iterator by default uses a greedy algorithm.

User may define custom algorithms for picking amongst segment options.

#### **Usage Model – Shadow Update/Checking**

- Each address map entry maintain shadow values for all its fields.

- Each region has a method for updating shadow value in any of its child entries:

```

update_shadow(trans : csco_addrmap_trans_s)

```

- Method will:

- check read response against shadow value.

- update shadow value, taking into account side-effects.

```

extend pci_monitor_u {

collect_trans_hook(tr : pci_trans_s) is also {

addrmap_trans = new csco_addrmap_trans_s with {

.opcode = (tr.dir == READ) ? READ : WRITE;

.target_region = tb_ptr.addrmap.get_physical_region("PCI");

.target_offset = tr.address;

.num_bytes = tr.data.size();

.data = tr.data;

.write_mask = tr.mask;

};

addrmap_trans.target_region.update_shadow(addrmap_trans);

};

};

```

### **Legacy Support**

- Task list for migrating legacy processor interface eVCs:

- sequence driver should extend the 'send\_addrmap\_item()' and 'addrmap\_read()' methods.

- create translation sequence that will use each addrmap transaction's iterator to launch multiple local transactions.

- extend monitor to call update\_shadow() of the appropriate addrmap region whenever a transaction is collected.